### CovVise: How We Stopped Throwing Away Interesting Coverage Data

http://www.veripool.org/papers/CovVise\_SNUGBos09\_pres.pdf

Wilson Snyder Cavium Networks wsnyder@wsnyder.org Robert Woods-Corwin NVIDIA covvise@rwoodsco.fastmail.fm

September 21, 2009

CovVise was created at and for SiCortex, Inc.

SiCortex formally closed in June 2009.

R.I.P.

- Tradition Dictates

And Our Deviations

- CovVise Language Extensions

- SystemC Extensions

- SystemVerilog Extensions

- CovVise Post-Simulation

- CovVise Database

- CovVise Web Interface

- Metrigator

- Conclusions

- Q&A

## Tradition: Verification Team Does It

- Traditionally,

- Only the Verification Team adds coverage

- Let the Designers also add coverage!

- They already add "line coverage"

- Just as they now add assertions, when writing RTL

- Fifo full, empty, unlikely cross products, bypasses

- Avoid duplication

- Some coverage is much easier when in RTL

- And some best left to the verification team (interfaces)

- Keep RTL simple... Later slides

• Traditionally,

CovVise

- Coverage is done near the end of the project

- Quantifies that little was missed

- (Test Driven Development == Write tests before code)

- Write the "test" of verification code, I.E. the coverage, FIRST!

- Saves writing focused test when random hits unexpected bins

- Focuses effort on big missing coverage items

- So find important bugs faster

- Reduces chance that interesting coverage cases are forgotten

- Provides good metric for management

• Traditionally,

CovVise

- Per bin, all test hits against that bin contribute to a single sum

- Which is better?

- 100 tests that hit a bin once?

- One test that hits a bin 100 times?

- Both count the same after aggregation some tools!

- Require some number of hits per test to count this bin as "covered"

- Prevents initialization-only from covering bins

- Insures good random or strong focused coverage

**1\*100** ≠ **100\*1**

"The Big Takeaway"

- Traditionally,

- Coverage is only collected on passing tests

- Failures shouldn't count towards coverage goals

**Tradition: Only Passing Tests Count**

- But learn from the Challenger disaster

Didn't graph failing cases, only successful ones

- If a bin is hit only by a failing test

- This bin is unlikely to be impossible

- This bin may indicate a bug is hiding behind it

- Conversely, fixing the failing test would improve coverage

- Focus effort on testing around this bin

- CovVise Language Extensions

- SystemC Extensions

- SystemVerilog Extensions

- CovVise Post-Simulation

- CovVise Database

- CovVise Web Interface

- Metrigator

- Conclusions

- Q&A

We extended SystemC to provide coverage ala SystemVerilog, via the <u>SystemPerl</u> pre-processor

```

SC_MODULE(myModule) {

// A SystemC Module

SP_COVERGROUP myGroup (

coverpoint myCoverPoint {

bins seven = 7;

// single value

bins three_to_five = [3:5]; // range

bins members of enum = enum type; // enum

};

);

void process() { // a method of the class

if (sampling_signal) { // when to sample

SP_COVER_SAMPLE(myGroup); // increment

```

• We also allow crosses, illegals (asserts) and ignores

```

SC_MODULE(myModule) {

SP_COVERGROUP myGroup (

coverpoint first {

bins three to five = [3:5];

};

coverpoint second[8] = [0:7];

cross myCross {

rows = {first};

cols = {second};

};

illegal bins func = myCross illegal()

ignore bins func = myCross ignore()

);

```

- RTL is procedural

- Coverage should be too... Alas the language doesn't allow this

- Allowed Designers to use \$ucover\_\* macros, for example

```

always @* begin

if (...) begin

$ucover_clk(clock, label)

```

• Vpassert (part of Verilog-Perl) expands this to:

```

reg _temp;

label: cover property (@(posedge clock) _temp)

always @* begin

_tempsig = 0;

if (...) begin

_tempsig = 1;

```

• Works with SV formal tools, too

- CovVise Language Extensions

- SystemC Extensions

- SystemVerilog Extensions

- CovVise Post-Simulation

- CovVise Database

- CovVise Web Interface

- Metrigator

- Conclusions

- Q&A

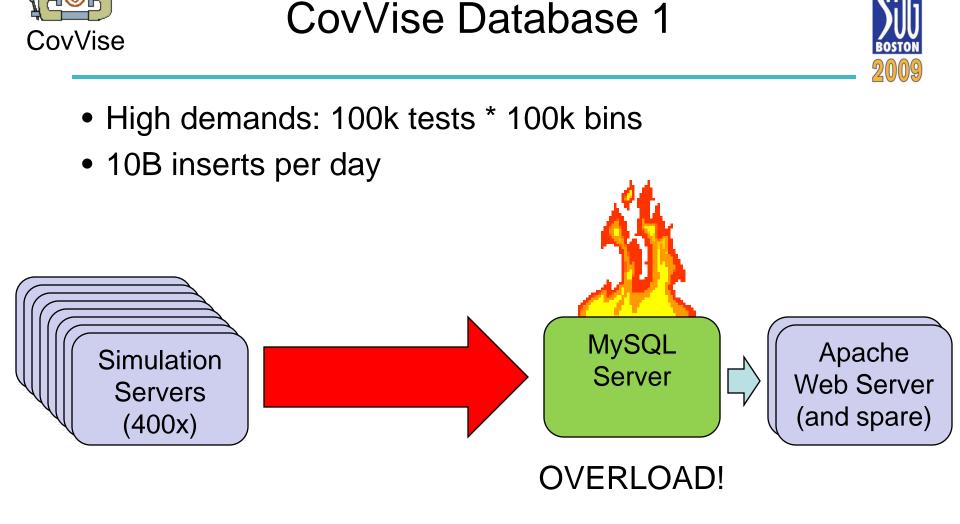

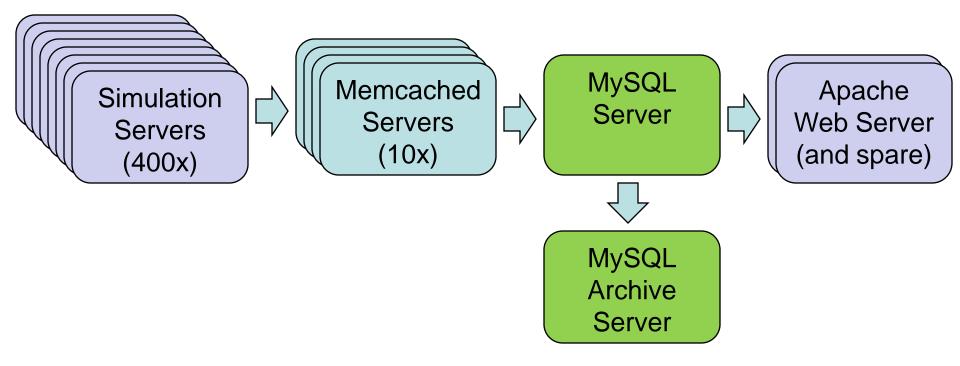

- High demands: 100k tests \* 100k bins

- 10B inserts per day

- Old data auto-pushed to archival database

- Users interface to CovVise data through the web

- "Simple enough even a VP can use it" ™ ☺

- Data is presented as hierarchy of coverage "pages"

- The interface begins with CovVise home page, which list "ensembles" of test runs...

Web: Ensembles

|   | A Home Ensembles & Vtestweb & Manpage & Help |                   |                |                                           |                  |           |                 |              |              |  |

|---|----------------------------------------------|-------------------|----------------|-------------------------------------------|------------------|-----------|-----------------|--------------|--------------|--|

|   | CovVise Er                                   | Isem              |                | ! – Only-failures bins<br>W – Waived bins |                  |           |                 |              |              |  |

| 6 | Ensembles                                    |                   |                | 1% - L<br>0% - H                          |                  | U         |                 |              |              |  |

|   | Only show rows                               | containing        | : 🗡            | Go                                        |                  | 7         |                 |              |              |  |

|   | Ensemble Name                                | <u>Testseries</u> | <u>Rev</u>     | <u>Start Time</u>                         |                  | Coverage  | <u>Bins</u>     | Tests        | <u>Files</u> |  |

|   | chip nightly                                 | ₽ <u>51689</u>    | @ <u>77547</u> | 05-20 00:46:48                            | <b>⊕</b> @(71.)  | .%) 58.0% | 1 <u>30,729</u> | <u>3,374</u> | <u>178</u>   |  |

|   | <u>chip_random</u>                           | ₽ <u>51543</u>    | @ <u>77511</u> | 05-19 14:26:26                            | <b>⊕</b> @(74.0  | )%) 66.6% | 129,016         | 20,286       | <u>155</u>   |  |

|   | <u>chip_random</u>                           | ₽ <u>51436</u>    | @ <u>77469</u> | 05-19 11:46:08                            | <b>(73.</b> :    | 2%) 65.5% | 129,016         | <u>6,630</u> | <u>155</u>   |  |

|   | <u>brett</u>                                 | @ <u>51432</u>    | @ <u>77469</u> | 05-19 11:39:50                            | ٠                | fails     | <u>109,363</u>  | 1            | <u>103</u>   |  |

|   | <u>brett</u>                                 | @ <u>51384</u>    | @ <u>77358</u> | 05-19 10:07:15                            | ٠                | fails     | <u>116,697</u>  | 3            | <u>104</u>   |  |

|   | <u>jason</u>                                 | @ <u>51377</u>    | @ <u>77468</u> | 05-19 10:02:31                            | (13.             | 7%) 8.9%  | 116,850         | 1            | <u>104</u>   |  |

|   | <u>brett</u>                                 | @ <u>51363</u>    | @ <u>77468</u> | 05-19 09:30:44                            | (14              | 3%) 9.6%  | <u>116,850</u>  | 3            | <u>104</u>   |  |

|   | chip_nightly                                 | @ <u>51328</u>    | @ <u>77459</u> | 05-19 00:23:56                            | <b>() (70.</b> 9 | 9%) 57.9% | 130,724         | 3,376        | <u>178</u>   |  |

Other formats: Detailed HTML

Web: Page Tree

#### Page tree under Ensemble 6Lycug

Source: CpyFPredictor.sp 433

| 🖃 Cpu                           | ⊕(66.1%) 54.7% <u>1(</u> | <u> 17,379 bins</u> |

|---------------------------------|--------------------------|---------------------|

| 🛨 Ebox                          | <b>(89.6%)</b> 76.4%     | <u>1,052 bins</u>   |

| - Fbox                          | <b>(40.5%)</b> 19.3%     | <u>56,256 bins</u>  |

| 🗄 bypassing                     | <b>(16.2%)</b> 1.9%      | 31,684 bins         |

| <u>cc_bits</u>                  | <b>()(93.7%)</b> 5.5%    | <u>144 bins</u>     |

| Page: sp_group/Cpu/Fbox/cc_bits | s                        |                     |

Cross of consumers of cc-bits are 2/3/4 cycles after updating the relevant cc-bits

|              |          | be           | twee      | en_ii    | nstru    | ıctio    | ns       |           |  |

|--------------|----------|--------------|-----------|----------|----------|----------|----------|-----------|--|

|              |          |              | rele      | van      | t_cc     | _bit     |          |           |  |

| consumer     |          |              |           | dl       | у3       |          |          |           |  |

|              | cc0      | cc1          | cc2       | cc3      | cc4      | cc5      | cc6      | cc7       |  |

| MOVF_D       | 1        | <u>5</u>     | 4         | <u>3</u> | 2        | <u>3</u> | <u>2</u> | <u>3</u>  |  |

| MOVF_PS      | <u>3</u> | <u>4</u>     | <u>0</u>  | 0        | <u>3</u> | <u>1</u> | <u>4</u> | <u>11</u> |  |

| MOVF_S       | 4        | 4            | <u>30</u> | <u>5</u> | <u>0</u> | <u>6</u> | 4        | Z         |  |

| MOVT_D       | 2        | <u>fails</u> | 2         | 4        | 2        | <u>3</u> | 2        | 1         |  |

| MOVT_PS      | 1        | <u>3</u>     | 4         | 3        | 2        | <u>1</u> | 3        | <u>3</u>  |  |

| MOVT_S       | <u>3</u> | 1            | Z         | 2        | 2        | 2        | <u>0</u> | 1         |  |

| exponen<br>x | ts_      | in_a         | add       |          |          |          |          |           |  |

### Web: Files

#### EListing of project/ver/chip/cpu/rbox/RboxCov.sp

| Line | v Count                                 | C++ Text                                                                                                                                      |  |  |  |  |  |  |  |

|------|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| 160  |                                         | SP_COVERGROUP RboxMulBypass (                                                                                                                 |  |  |  |  |  |  |  |

| 161  |                                         | description = "Rbox Bypass Coverage";                                                                                                         |  |  |  |  |  |  |  |

| 162  |                                         | page = "Cpu/Rbox";                                                                                                                            |  |  |  |  |  |  |  |

| 163  |                                         |                                                                                                                                               |  |  |  |  |  |  |  |

| 164  | coverpoint cov_mul_mux_operand(MuxOp) { |                                                                                                                                               |  |  |  |  |  |  |  |

| 165  |                                         | bins MulA = RBoxMux::Ea;                                                                                                                      |  |  |  |  |  |  |  |

| 166  |                                         | <pre>bins MulB = RBoxMux::Eb;</pre>                                                                                                           |  |  |  |  |  |  |  |

| 167  |                                         | illegal_bins unlucky = default;                                                                                                               |  |  |  |  |  |  |  |

| 168  |                                         | };                                                                                                                                            |  |  |  |  |  |  |  |

| 169  |                                         | coverpoint cov_mul_bypass_src(Bypass) {                                                                                                       |  |  |  |  |  |  |  |

| 170  |                                         | auto_enum_bins = RBoxByp;                                                                                                                     |  |  |  |  |  |  |  |

| 171  |                                         | ignore_bins_func = bypass_src_ignore();                                                                                                       |  |  |  |  |  |  |  |

| 172  |                                         | };                                                                                                                                            |  |  |  |  |  |  |  |

| 173  |                                         |                                                                                                                                               |  |  |  |  |  |  |  |

| 174  |                                         | cross MulBypass {                                                                                                                             |  |  |  |  |  |  |  |

|      | (100.0%) 88.8%                          |                                                                                                                                               |  |  |  |  |  |  |  |

|      |                                         | <u>Show Table</u><br>1,703 col0=M3, hier=top.board.pred.cpuRPred0.coverage, row0=MulA                                                         |  |  |  |  |  |  |  |

|      |                                         | 1,703 colo=M3, hier=top.board.pred.cpuRPred0.coverage, rowo=MulA                                                                              |  |  |  |  |  |  |  |

|      |                                         | 85 col0=M4, hier=top.board.pred.cpuRPred0.coverage, row0=MulA                                                                                 |  |  |  |  |  |  |  |

|      |                                         | <u>112</u> colO=M4, hier=top.board.pred.cpuRPredO.coverage, rowO=MulB                                                                         |  |  |  |  |  |  |  |

|      |                                         | 16 colO=MW, hier=top.board.pred.cpuRPredO.coverage, rowO=MulA                                                                                 |  |  |  |  |  |  |  |

|      |                                         | <u>8</u> col0=MW, hier=top.board.pred.cpuRPred0.coverage, row0=MulB<br>70,093 col0=REGFILE, hier=top.board.pred.cpuRPred0.coverage, row0=MulA |  |  |  |  |  |  |  |

|      |                                         | 70,389 col0=REGFILE, hier=top.board.pred.cpuRPred0.coverage, row0=MulA                                                                        |  |  |  |  |  |  |  |

| 175  |                                         | rows = {MuxOp};                                                                                                                               |  |  |  |  |  |  |  |

| 176  |                                         | cols = {Bypass};                                                                                                                              |  |  |  |  |  |  |  |

| 177  |                                         | };                                                                                                                                            |  |  |  |  |  |  |  |

| 178  |                                         | ); /*RboxMulBypass*/                                                                                                                          |  |  |  |  |  |  |  |

|      |                                         |                                                                                                                                               |  |  |  |  |  |  |  |

Web: Binruns 1

#### Coverage Details for Binrun k1YyKA

| CumCover | Category              | Tests       | Count |

|----------|-----------------------|-------------|-------|

| 0.0%     | Pass High-Count       | 0           | 0     |

| 100.0%   | Pass Low-Count (< 10) | 9           |       |

| 0.0%     | Pass Waived           | ss Waived 0 |       |

| 0.0%     | Pass Zero-Count       | 1,642       | 0     |

|          | Fail Non-Zero-Count   | 0           | 0     |

|          | Fail Zero-Count       | 686         | 0     |

| 100.0%   | TOTAL                 | 2,331       | 9     |

Similar table is also poped-up when mouse hovers over any coverage data.

#### Other Ensembles With Bin vWot1Q

Tests with Binrun k1YyKA

Web: Binruns 2

## Coverage Details for Binrun k1YyKA Other Ensembles With Bin vWot1Q

| <u>Binrun Id</u> | Ensemble Name       | <u>Start Time</u> | <u>Coverage</u>      | <u>Count</u> | Tests         |

|------------------|---------------------|-------------------|----------------------|--------------|---------------|

| <u>1LPAFg</u>    | <u>chip nightly</u> | 05-15 00:30:29    | <u>100.0%</u>        | 27           | <u>2,319</u>  |

| <u>3SxlGw</u>    | <u>chip random</u>  | 05-17 46:39       | <u>(100.0%) 0.0%</u> | <u>20</u>    | <u>22,450</u> |

| <u>k1YyKA</u>    | THIS                | 05-20 00. 🔫       | <u>(100.0%) 0.0%</u> | <u>9</u>     | <u>2,331</u>  |

| <u>LkW0rA</u>    | <u>chip random</u>  | 05-14 13:29.      | 9.0%) 0.0%           | <u>9</u>     | <u>13,061</u> |

| SouRCQ           | <u>chip nightly</u> | 05-17 00:32:2     | 0.0%                 | <u>8</u>     | <u>2,924</u>  |

| Page: 1 2        | <u>34 All</u>       |                   | $\overline{\ }$      |              |               |

### Tests with Binrun k1YyKA Solves:

"I know I've seen this bin hit some previous night"

Web: Binruns 3

# •Coverage Details for Binrun k1YyKA •Other Ensembles With Bin vWot1Q

| <u>Binrun Id</u> | Ensemble Name       | <u>Start Time</u> | <u>Coverage</u>            | <u>Count</u> | Tests  |         |  |  |  |  |

|------------------|---------------------|-------------------|----------------------------|--------------|--------|---------|--|--|--|--|

| <u>1LPAFg</u>    | <u>chip_nightly</u> | 05-15 00:30:29    | <u>100.0%</u>              | 27           | 2,319  |         |  |  |  |  |

| <u>3SxlGw</u>    | <u>chip_random</u>  | 05-17 11:46:39    | (100.0%) 0.0%              | 20           | 22.450 |         |  |  |  |  |

| <u>k1YyKA</u>    | THIS                | 05-20 00:46:      | What tests hit this bin, a |              |        |         |  |  |  |  |

| <u>LkW0rA</u>    | <u>chip_random</u>  | 05-14 13:29:      |                            |              |        | · · · · |  |  |  |  |

| SouRCQ           | <u>chip_nightly</u> | 05-17 00:32:      | did the                    | y pas        | s or i |         |  |  |  |  |

| Page: 1 🛛        | 2 <u>3 4 All</u>    |                   |                            |              |        |         |  |  |  |  |

#### Tests with Binrun k1YyKA #

| <u>Binrun Id</u> | <u>Test Name</u>                                  | Seed   | <u>Status</u> | <u>Count</u> |

|------------------|---------------------------------------------------|--------|---------------|--------------|

| <u>k1YyKA</u>    | <u>cpu_idefm_rtl/avp=add.d,mode=EL-M64R2-U</u>    | 628065 | Pass          | 4            |

| <u>k1YyKA</u>    | <u>cpu_idefm_rtl/avp=add.d,mode=EL-M64R2-K</u>    | 410295 | Pass          | 4            |

| <u>k1YyKA</u>    | <u>cpu_idefm_rtl/mg,src=fboxAddSubMul</u>         | 572271 | Pass          | 1            |

| <u>k1YyKA</u>    | <u>cpu fpipe/cpu cpp,src=fbox demo s</u>          | 983400 | Pass          | 0            |

| <u>k1YyKA</u>    | <u>cpu fpipe/cpu cpp,src=fboxa madd bug</u>       | 449504 | Pass          | 0            |

| <u>k1YyKA</u>    | <u>cpu_subrtl/mg,src=everything,instrs=5k</u>     | 317175 | Pass          | 0            |

| <u>k1YyKA</u>    | <u>cpu_idefm_rtl/cpu_cpp,src=llsc1</u>            | 606318 | Fail          | 0            |

| <u>k1YyKA</u>    | <u>cpu idefm rtl/cpu cpp,src=cp0 error dcache</u> | 541852 | Fail          | 0            |

| <u>k1YyKA</u>    | <u>cpu_subrtl/mg,src=everything,instrs=5k</u>     | 91087  | Fail          | 0            |

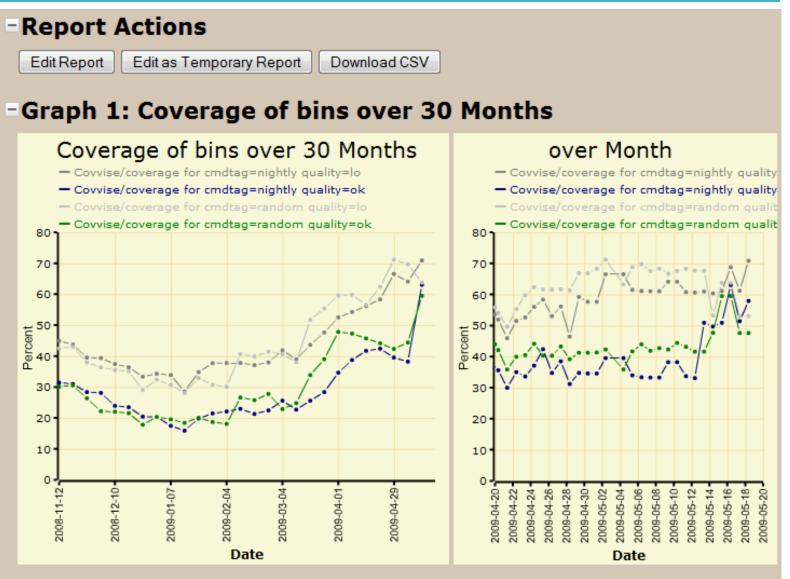

- Metrigator: Our verification metrics database

- CovVise coverage (percent low coverage, ok coverage, number of bins)

- Bug count (total, closed, per-component, by priority, etc)

- Bug closure rate (total, per-component, by priority, etc)

- Source code commits (size, number of edits)

- Verification test success (number of tests, failures)

- Spots Correlated Trends

- Appeases Management ©

Metrigator Coverage Graph

- CovVise Language Extensions

- SystemC Extensions

- SystemVerilog Extensions

- CovVise Post-Simulation

- CovVise Database

- CovVise Web Interface

- Metrigator

- Conclusions

- Q&A

## Conclusions

- Verification Engineers got

- SystemC extended with SystemVerilog-ish coverage

- Data collected on failing tests, to easily detect interesting bins

- Designers got

- Coverage as part of normal RTL procedural statements

- Easy browsing of data

- Management got

- Early coverage for progress tracking and work reduction

- Pretty graphs

- If we were to do it again?

- Start coverage insertion even earlier

- [SiCortex,] Don't run out of money ©

- The open source design tools are available at <u>http://www.veripool.org</u>

- These slides + paper at <u>http://www.veripool.org/papers/</u>

- CovVise Have you been paying attention?

- SystemPerI /\*AUTOs\*/ for SystemC

- Verilog-Perl Toolkit with Preprocessing, Renaming, etc

- Verilator Compile SystemVerilog into SystemC

- Additional Tools

- Make::Cache Object caching for faster compiles

- Schedule::Load Load Balancing (ala LSF)

- Verilog-Mode for Emacs /\*AUTO...\*/ Expansion

- Vregs Extract register and class declarations from documentation